# DIY: **PROJECT**

# **PLL FM Transmitter**

#### **JOY MUKHERJI**

his is a circuit that offers a challenge to electronics enthusiasts and hobbyists—an FM transmitter that uses readily available components and covers the FM broadcast

band in 100kHz steps. The frequency drift is controlled by phase-locked-loop

(PLL) method, making transmission frequency rock-solid all the time, just like commercial stations. Using DIP switches, simply punch in the frequency on which you wish to broadcast, and you are on the air.

### **Circuit and working**

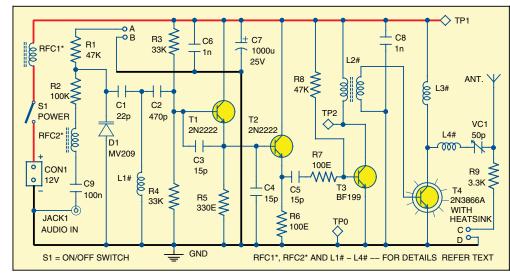

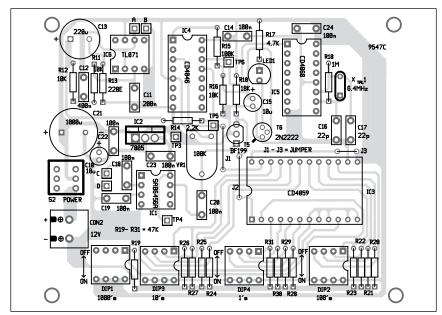

The circuit comprises two units. Unit 1 is the RF section of the transmitter, shown in Fig. 1, which transmits the

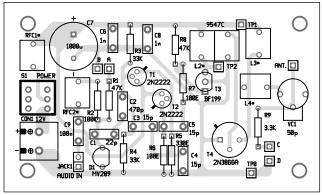

> FM signal. Unit 2 is the PLL control section, shown in Fig. 2, which helps in locking the transmission frequency. The circuit uses phase-lock loop that provides drift-free transmission frequency.

> The RF section is built around transistors T1-T4, with T1 (2N2222) in Colpitts oscillator configuration. The frequency of the oscillator is determined by coil L1 and capacitors C1, C2, C3 and C4. Modulating signal, which is in audio range, is fed through Jack1. D1 is a varactor diode,

working in reverse-bias mode. Since this is an FM transmitter, the deviation in the frequency of the oscillator is based on the amount of reverse-bias generated by the audio signal. Transistor T2 (2N2222) acts as a buffer that isolates the oscillator from the rest of the amplifier chain.

Frequency-modulated signal is coupled to driver transistor T3 (BF199) via capacitor C5. R7 is a current-limiting resistor. Transistor T3 is wired as a Class A amplifier and drives transistor T4 (2N3866A) via broadband impedance matching transformer L2. Power amplifier operates in Class B mode. Coil L4 and trimmer capacitor VC1 match transistor T4's collector to the antenna.

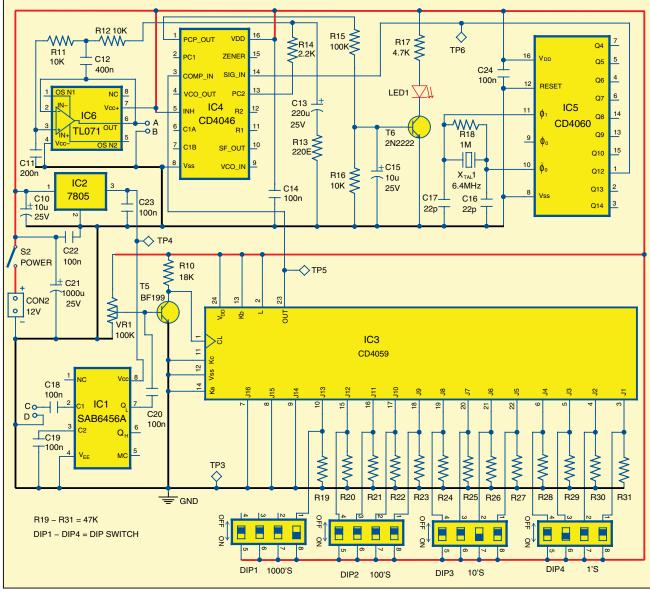

The PLL control section is built around 64/256 prescaler SAB6456A (IC1), programmable divide-by-N counter CD4059(IC3), phase lockedloop comparator CD4046 (IC4), 14-stage ripple carry binary counter/oscillator

Fig. 1: RF section of the transmitter (Unit 1)

| PARTS LIST                            |                                            |                    |                                                             |

|---------------------------------------|--------------------------------------------|--------------------|-------------------------------------------------------------|

| Semiconductors                        |                                            | C2                 | - 470pF ceramic disk                                        |

| IC1                                   | - SAB6456A 64/256 prescaler                | C3-C5              | - 15pF ceramic disk                                         |

| IC2                                   | - 7805 voltage regulator                   | C6, C8             | - 1nF ceramic disk                                          |

| IC3                                   | - CD4059 programmable                      | C7, C21            | - 1000µF, 25V electrolytic                                  |

|                                       | divide-by-N counter                        | C9, C14,           | • •                                                         |

| IC4                                   | - CD4046 phase-locked-loop                 | C18-C20, C22,      |                                                             |

|                                       | (PLL) comparator                           | C24                | - 100nF ceramic disk                                        |

| IC5                                   | - CD4060 ripple carry binary               | C10, C15           | <ul> <li>10µF, 25V electrolytic</li> </ul>                  |

|                                       | counter/oscillator                         | C11                | - 200nF ceramic disk                                        |

| IC6                                   | - TL071 operational amplifier              | C12                | - 400nF ceramic disk                                        |

| T1, T2, T6                            | - 2N2222 npn transistor                    | C13                | - 220µF, 25V electrolytic                                   |

| T3, T5                                | <ul> <li>BF199 npn transistor</li> </ul>   | VC1                | <ul> <li>50pF trimmer capacitor</li> </ul>                  |

| T4                                    | <ul> <li>2N3866A npn transistor</li> </ul> | Miscellaneous:     |                                                             |

| D1                                    | <ul> <li>MV209 varactor diode</li> </ul>   | RFC1               | - 50T, 28SWG balun core                                     |

| LED1                                  | - 5mm LED                                  | RFC2               | - 25T, 28SWG balun core                                     |

| Resistors (all 1/4-watt, ±5% carbon): |                                            | L1                 | - 4T, 4mm dia 26SWG                                         |

| , ,                                   | 1 - 47-kilo-ohm                            | L2                 | <ul> <li>Broadband transformer</li> </ul>                   |

| R2, R15                               | - 100-kilo-ohm                             |                    | 6T primary 26SWG,                                           |

| R3, R4                                | - 33-kilo-ohm                              |                    | 1T secondary, 20SWG                                         |

| R5                                    | - 330-ohm                                  | L3                 | - 13T, 8mm dia 26SWG                                        |

| R6, R7                                | - 100-ohm                                  |                    | air core                                                    |

| R9                                    | - 3.3-kilo-ohm                             | L4                 | - 6T, 8mm dia 26 SWG                                        |

| R10                                   | - 18-kilo-ohm                              |                    | air core                                                    |

| R11, R12, R16                         | - 10-kilo-ohm                              | CON-CON2           | - 2-pin terminal connector                                  |

| R13                                   | - 220-ohm                                  | X <sub>TAL</sub> 1 | - 6.4MHz crystal                                            |

| R14                                   | - 2.2-kilo-ohm                             | DIP1-DIP4          | - DIP switch                                                |

| R17<br>R18                            | - 4.7-kilo-ohm                             | S1, S2             | <ul> <li>On/off switch</li> <li>Audio input jack</li> </ul> |

| VR1                                   | - 1-mega-ohm<br>- 100-kilo-ohm preset      |                    | - Co-axial cable                                            |

|                                       | - 100-kilo-onin preset                     |                    | - Co-axial cable<br>- Heat sink for transistor T4           |

| Capacitors:                           | 22 F 111                                   |                    | - Wire antenna                                              |

| C1, C16, C17                          | - 22pF, ceramic disk                       | I                  | - wite anteinid                                             |

72 DECEMBER 2014 | ELECTRONICS FOR YOU

## DIY: **PROJECT**

Fig. 2: PLL control section (Unit 2)

CD4060 (IC5) and operational amplifier TL071 (IC6).

This section uses voltage regulator 7805 (IC2) to provide regulated power supply of 5V for the working of IC1. IC5 generates 1.5625kHz reference frequency for the PLL at pin 1, which is fed to frequency comparator (IC4) at pin 14.

A low-level output is taken from the antenna via limiting resistor R9 (shown in Fig. 1), which is coupled to pin 2 of IC1 via capacitor C18. Pin 5 of IC1, the mode pin, is left open to select divide-by-64 mode. Output frequency of the transmitter is divided by 64. Transistor T5 converts the output of IC1 to 12V CMOS levels. The signal is further divided in programmable divide-by-N counter CD4059 (IC3). Output of CD4059 (pin 23) is connected to the frequency comparator pin 3 of IC4. The PLL comparator (IC4) compares the phase relationship between the reference signal on pin 14 with the input frequency on pin 3.

Depending upon the variance (phase relationship) up or down, a correction voltage is generated on pin 13 of IC4, which is applied to the varactor diode of the VCO to bring it precisely to 'on frequency.' An active low-pass filter (IC6) removes audible 1.5625kHz reference tone from the control voltage.

## **PLL Transmitter Test Points**

| Test point                            | Details                       |  |

|---------------------------------------|-------------------------------|--|

| TP0, TP3                              | OV (GND)                      |  |

| TP1                                   | +12V                          |  |

| TP2                                   | Transmitted frequency         |  |

| TP4                                   | +5V                           |  |

| TP5                                   | Frequency as set by DIP1-DIP4 |  |

| TP6                                   | 1.5625kHz                     |  |

| Note: All measurements are w.r.t. GND |                               |  |

The reference frequency of the PLL is multiplied by the programmable divider divide rate to give the final frequency. If the divider rate is 1024 (as set by DIP switches DIP1-DIP4

## DIY: PROJECT

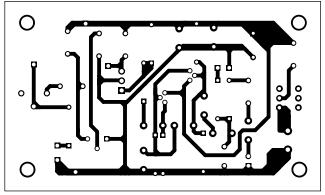

Fig. 3: Actual-size PCB layout of RF section

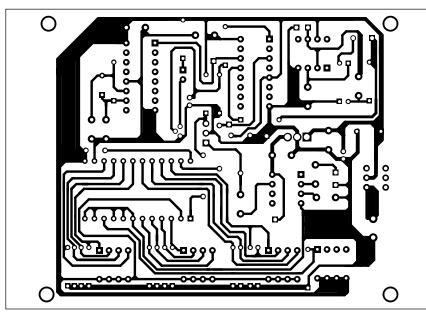

Fig. 5: Actual-size PCB layout of PLL control section

Fig. 6: Component layout of PCB of PLL control section

Fig. 4: Component layout of PCB of RF section

shown in Fig. 2), then the output will be  $1.5625 \times 1024 \times 64 = 102.4$  MHz.

Similarly, a DIP setting of 1000 gives us an output frequency of 100MHz. LED1 lights up to indicate a lock on the selected frequency.

#### **Construction and testing**

An actual-size, single-layer PCB layout for Unit 1 is shown in Fig. 3 and its component layout in Fig. 4. Singlelayer, actual-size PCB layout for Unit 2 is shown in Fig. 5 and its component layout in Fig. 6.

Assemble the circuits on the PCBs to save time and minimise assembly errors. Unit 1 is connected to Unit 2 by a co-axial cable of short length. Open end of resistor R1, indicated as 'A' in Unit 1, is connected to pin 6 of IC6, indicated as 'A' in Unit 2, by co-axial cable. Similarly, open end of resistor R9, indicated as 'C' in Unit 1, is connected to open end of C18, indicated as 'C' in Unit 2, by co-axial cable. Ground the shield wire of the coaxial cable.

Keep all leads as short as possible. To test the circuit for proper functioning, connect stabilised 12V supply to both the units. The circuit will accept audio signal from just about anything (CD, tape, iPod or computer) and transmit the signal, which can be received by an FM radio. An external microphone amplifier can be used for speech. A good matching 50-ohm ground-plane antenna will greatly enhance the range of transmission. Use appropriate IC bases on the PCB.

The author is an electronics hobbyist and a smallbusiness owner in Albany, New York, USA. His interests include designing RF circuits