# SONY

#### Cable Equalizer with 2-system Switching Function

# **CXB1441R**

#### **Description**

The CXB1441R is a cable equalizer that compensates the attenuation resulting from cable transfer of small-amplitude differential NRZ signals.

This chip has two sets of input ports comprising three pairs of differential data signals and one pair of differential clock signals. It equalizes and quantizes the signals from the optional ports and then outputs the signal from the output ports. NRZ signals from 250Mb/s to 1.65Gb/s are supported.

(Applications: High-speed digital video signal switching and compensation of cable attenuation)

#### **Features**

- ◆ Two sets of input ports comprising three pairs of differential data signals and one pair of differential clock signals

- lackloss 50 $\Omega$  termination pull-up resistors built into differential data and clock inputs

- Low differential data and clock input capacitance facilitates the design and manufacture of TDR standard compatible equipment

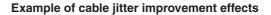

- ◆ Equalizer circuit that compensates cable attenuation improves the signal eye pattern

- ♦ Output 50Ω load drive, voltage amplitude 0.5Vp-p

- ◆ Single +3.3V power supply

- ◆ Low power consumption

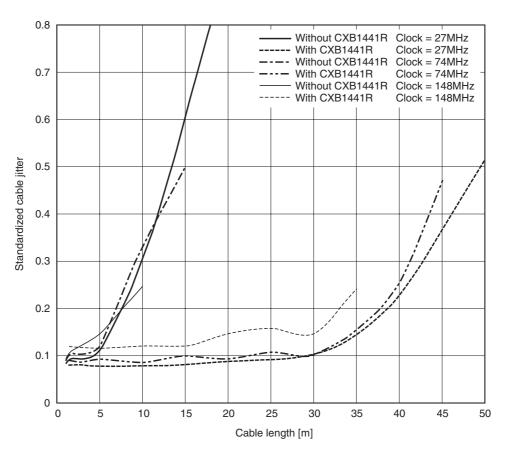

- ◆ Lead-free 48-pin plastic LQFP package (7mm × 7mm)

#### **Package**

48-pin LQFP (Plastic)

#### **Absolute Maximum Ratings**

◆ Supply voltage

Vcc −0.3 to +4.0

V

◆ Storage temperature

Tstg −65 to +150

°C

#### **Recommended Operating Conditions**

Supply voltage

Vcc

3.135 to 3.465

V

Operating temperature

Ta

-20 to +75

°C

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

- 1 - E05516-PS

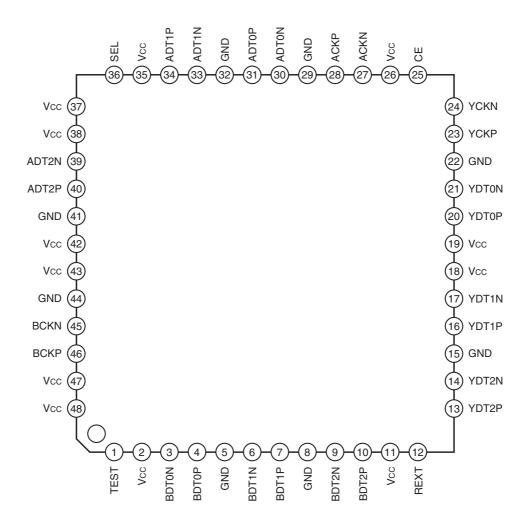

### **Pin Configuration**

# Pin Description

| Pin No.                                                      | Symbol | Туре            | Equivalent circuit    | Description                                      |  |

|--------------------------------------------------------------|--------|-----------------|-----------------------|--------------------------------------------------|--|

| 2, 11,<br>18, 19,<br>26, 35,<br>37, 38,<br>42, 43,<br>47, 48 | Vcc    | Power<br>supply | Vcc                   | Power supply. Connect to $3.3\text{V} \pm 5\%$ . |  |

| 5, 8,<br>15, 22,<br>29, 32,<br>41, 44                        | GND    | GND             | Vcc                   | GND.<br>Connect to 0V.                           |  |

| 28                                                           | ACKP   | Differential    |                       | A port differential clock input.                 |  |

| 27                                                           | ACKN   | input           | GND                   |                                                  |  |

| 31                                                           | ADT0P  | Differential    |                       | A port differential data input 0.                |  |

| 30                                                           | ADT0N  | input           | (31) - W - (30) - GND | 7 port differential data input o.                |  |

| 34                                                           | ADT1P  | Differential    |                       | A port differential data input 1.                |  |

| 33                                                           | ADT1N  | input           | 34 W 33 GND           | 7. port dinordinal data input 1.                 |  |

| 40                                                           | ADT2P  | Differential    | ADT2P ADT2N           | A port differential data input 2.                |  |

| 39                                                           | input  |                 | 40 W 39 GND           | A port dinordiniar data input 2.                 |  |

| Pin No. | Symbol | Туре         | Equivalent circuit          | Description                                                       |  |

|---------|--------|--------------|-----------------------------|-------------------------------------------------------------------|--|

| 46      | ВСКР   | Differential | Vcc<br>BCKP BCKN<br>46 W 45 | B port differential clock input.                                  |  |

| 45      | BCKN   | input        | GND                         |                                                                   |  |

| 4       | BDT0P  | Differential | Vcc<br>BDT0P BDT0N          | P part differential data input 0                                  |  |

| 3       | BDT0N  | input        | 4 W 3 GND                   | B port differential data input 0.                                 |  |

| 7       | BDT1P  | Differential | Vcc<br>BDT1P BDT1N          | B port differential data input 1.                                 |  |

| 6       | BDT1N  | input        | GND GND                     | ,                                                                 |  |

| 10      | BDT2P  | Differential | Vcc<br>BDT2P BDT2N          | B port differential data input 2.                                 |  |

| 9       | BDT2N  | input        | GND GND                     | b port uniferential data input 2.                                 |  |

| 25      | CE     | CMOS in      | Vcc<br>CE<br>25<br>GND      | Chip enabled by High input.                                       |  |

| 36      | SEL    | CMOS in      | SEL GND                     | A ports selected by High input,<br>B ports selected by Low input. |  |

| Pin No. | Symbol | Туре         | Equivalent circuit | Description                                                                     |  |

|---------|--------|--------------|--------------------|---------------------------------------------------------------------------------|--|

| 12      | REXT   | Analog       | Vcc<br>REXT O GND  | Connect to GND through a $4.7k\Omega\pm1\%$ input impedance adjusting resistor. |  |

| 1       | TEST   | CMOS in      | Vcc<br>TEST P      | Test function control.<br>Fix Low.                                              |  |

| 23      | YCKP   | Differential | VCKP YCKN 23       | Differential clock output.                                                      |  |

| 24      | YCKN   | output       | GND                |                                                                                 |  |

| 20      | YDT0P  | Differential | Vcc<br>YDTOP YDTON | Differential data output 0.                                                     |  |

| 21      | YDT0N  | output       | out 20 21 GND      | •                                                                               |  |

| 16      | YDT1P  | Differential | Vcc<br>YDT1P YDT1N | Differential data output 1.                                                     |  |

| 17      | YDT1N  | output       | 16 T7 GND          | Dinordinar data output 1.                                                       |  |

| 13      | YDT2P  | Differential | Vcc<br>YDT2P YDT2N | Differential data output 2.                                                     |  |

| 14      | output |              | 13<br>GND          | 2oroman data odiput 2.                                                          |  |

#### **Electrical Characteristics**

#### DC characteristics

(Under the recommended operating conditions)

| Item                                              | Symbol | Min.      | Тур. | Max.      | Unit | Remarks                            |

|---------------------------------------------------|--------|-----------|------|-----------|------|------------------------------------|

| CMOS input High level voltage                     | VIH_M  | Vcc - 0.5 |      | Vcc + 0.3 | V    |                                    |

| CMOS input Low level voltage                      | VIL_M  | -0.3      |      | 0.5       | V    |                                    |

| CMOS input High level current                     | IIH_M  |           |      | 1         | μА   | @VIN = Vcc                         |

| CMOS input Low level current                      | IIL_M  | -1        |      |           | μА   | @VIN = 0                           |

| Differential input pin resistance relative to Vcc | RTERM  | 45        | 50   | 55        | Ω    | @CE = Vcc,<br>IIN = -10mA, *1      |

| Differential input dynamic range                  | VI     | Vcc - 0.8 |      | Vcc + 0.2 | V    |                                    |

| Differential output High level current            | ЮН     | 0         |      | 0.05      | mA   |                                    |

| Differential output Low level current             | IOL    | 8         | 10   | 12        | mA   |                                    |

| Supply current (operating)                        | Icc    | 110       |      | 165       | mA   | CE = H,<br>differential input open |

| Supply current (standby)                          | Istby  |           |      | 30        | μA   | CE = L,<br>differential input open |

<sup>\*1</sup> The resistance value when CE = Low is  $55\Omega$  (typ.).

#### **AC Characteristics**

(Under the recommended operating conditions)

| Item                        | Symbol | Min. | Тур. | Max. | Unit | Remarks                         |

|-----------------------------|--------|------|------|------|------|---------------------------------|

| Clock frequency             | fCK    | 25   |      | 165  | MHz  | 1/10 the differential data rate |

|                             |        | 5    |      |      | dB   | @125MHz                         |

| Maximum equalizer gain      | G_EQ   | 6    |      |      | dB   | @200MHz                         |

| iviaximum equalizer galir   | G_EQ   | 9    |      |      | dB   | @400MHz                         |

|                             |        | 12   |      |      | dB   | @740MHz                         |

| Differential data and clock | Tr     |      | 150  |      | ns   | 20 to 80%                       |

| output rise/fall time       | Tf     |      | 150  |      | ns   | 80 to 20%                       |

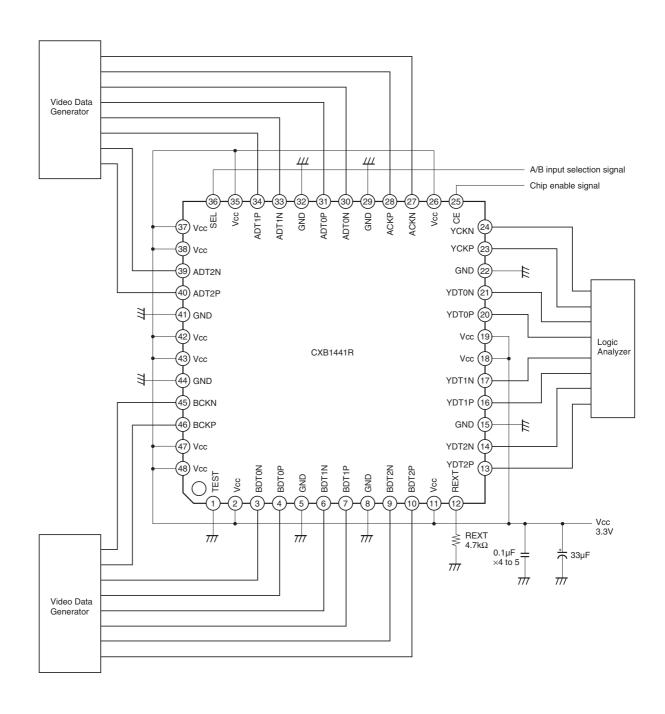

#### **Electrical Characteristics Measurement Circuit**

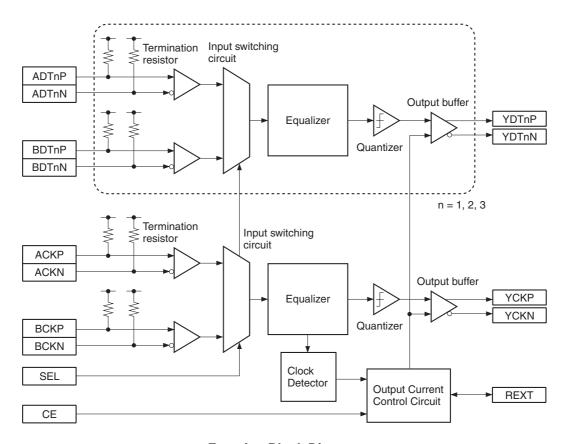

#### **Description of Functions**

The CXB1441R has two sets of input ports comprising three pairs of differential data signals and one pair of differential clock signals. The A ports are selected when a High signal is applied to the CMOS input pin SEL, and the B ports are selected when a Low signal is applied. Shaping is performed by the equalizer to compensate the signal deterioration of the selected port data signals and clock signals caused by transfer cable attenuation, and then these signals are quantized and reproduced on the output ports.

The CXB1441R inputs have built-in  $50\Omega$  pull-up resistors that act as transfer termination resistors, and parasitic capacitance is suppressed to a level that does not deteriorate the TDR characteristics of the equipment.

The outputs employ a 10mA differential current output format in order to drive external  $50\Omega$  pull-up resistors. This output current is driven only when a High signal is applied to the CMOS input pin CE and the clock signal of the selected input port is in differential mode.

When a Low signal is applied to the CMOS input pin CE, the CXB1441R enters standby mode to reduce the power consumption.

The CXB1441R can be controlled by operating only the CMOS input pins CE and SEL.

**Function Block Diagram**

SONY CXB1441R

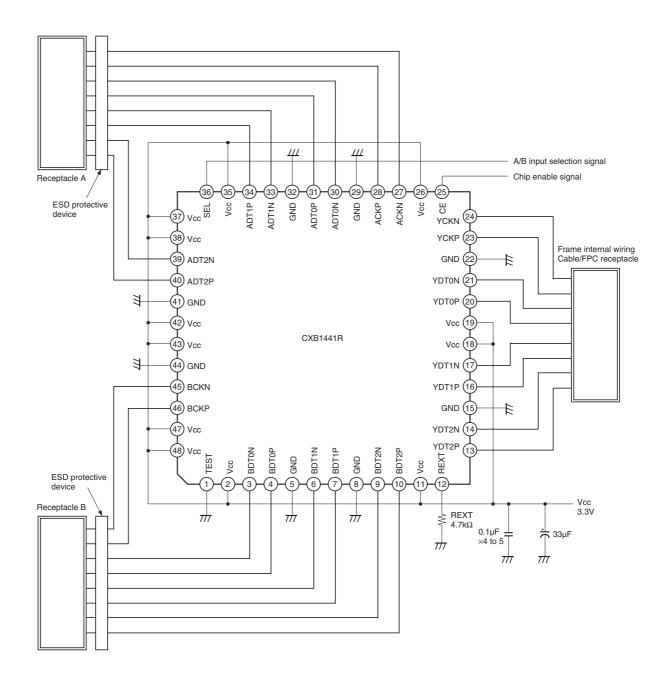

#### **Application Circuit**

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

#### **Equalizer Characteristics**

#### **Notes On Handling**

The guideline for cable attenuation that can be compensated by the equalizer is the maximum equalizer gain. However, this rule does not apply when skin effects cause the attenuation characteristics to deviate greatly from the square root of the frequency response, or for cables with a large skew.

## **Package Outline**

(Unit: mm)

#### 48PIN LQFP (PLASTIC)

NOTE: Dimension "\*" does not include mold protrusion.

PACKAGE STRUCTURE

# SONY CODE LQFP-48P-L01 EIAJ CODE P-LQFP48-7x7-0.5

JEDEC CODE

| PACKAGE MATERIAL | EPOXY RESIN       |

|------------------|-------------------|

| LEAD TREATMENT   | PALLADIUM PLATING |

| LEAD MATERIAL    | COPPER ALLOY      |

| PACKAGE MASS     | 0.2g              |