### Scalable Compiler Optimizations for Improving the Memory System Performance in Multi- and Many-core Processors

## A THESIS SUBMITTED TO THE FACULTY OF THE GRADUATE SCHOOL OF THE UNIVERSITY OF MINNESOTA

BY

Sanyam Mehta

### IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

**Pen-Chung Yew**

September, 2014

© Sanyam Mehta 2014 ALL RIGHTS RESERVED

# Acknowledgements

I would first of all acknowledge my Teachers for molding the direction of my life's path, especially when I had entered my Bachelor's and needed such clear guidance the most. Not only was I introduced to research by them, but was also, more importantly, taught the utility of the education that I was getting. I have ever since been clear about things to do next that will benefit me and others, and thus contribute positively in a little way to the society.

As a PhD student, I feel that I was blessed to have Professor Yew as my advisor. Right from the beginning, he encouraged and helped me to choose the right problems to work on, and was always there to provide me with the right guidance at the right moments based on his vast experience of our research area. In addition, I would also like to extend my heartfelt thanks to Professor Zhai, for helping me refine my work and make it appealing to the target audience. She has especially been very helpful in teaching me to make presentations for conferences. Also, I would thank, Professor Kumar for always being very warm and accomodating throughout my stay at the University of Minnesota and while serving as a member on my committee, and Professor David Lilja, Professor Stephen McCamant, Professor Daniel Boley and Dr. Aamer Jaleel for honoring me with their presence during my thesis defense and asking me insightful questions.

I would also thank my very dear friends, Ankit, Ashish, Ayush, Rajat, Saket, and Shashank for helping me in various ways to stay focused towards my goal in life. It is because of being happy in their presence that I could work effectively at college.

Finally, I would thank my parents, brother, and also other family members. They first of all cared for me and taught me all that I knew until I grew up and could think about things, and then allowing me to be in a different country for my PhD. They have been very understanding and accomodating to allow me to do something that I thought would be helpful for all, and have always encouraged me and blessed me to be successful.

# Dedication

To my Teacher and Parents

#### Abstract

The last decade has seen the transition from unicore processors to their multi-core (and now many-core) counterparts. Today, multi-cores are ubiquitous - they form the core fabric of our laptop and desktop PCs, supercomputers, datacenters, and also mobile devices. This transition has brought about renewed focus on compiler developers to extract performance from these parallel processors. In addition to extracting parallelism, another important responsibility of a parallelizing (or optimizing) compiler is to improve the memory system performance of the source program. This is particularly important because all cores on the chip simultaneously demand for data from the slow memory, and thus computation ends up waiting for the arriving data. In other words, the multi-cores have accentuated the *memory-wall*. These simultaneous requests for data from off-chip memory also leads to contention for bandwidth in off-chip network (called *bandwidth wall*), leading to further increase in the effective memory latency as seen by the executing program.

While the above responsibilities of a parallelizing compiler are better understood, we identify three key challenges facing the compiler developers on current processors. These include, (1) the diverse set of microarchitectures existent at any time, and more importantly, the changes in micrarchitecture between generations. We identify that the existing compilers have particularly been unable to adapt to some of the important changes to microarchitecture in the last decade, resulting in suboptimal optimizations. (2) Poor show of compilers in real applications that contain large scope of statements amenable for optimization. This weakness stems from the lack of a good cost model for deciding statements to fuse, and sheer inability to fuse due to ineffective dependence analysis. (3) Unscalability of compilers - this is a traditional limitation of compilers where the compilers choose to optimize small scopes to contain the compile time and memory requirement, and thus loose optimization opportunities.

In this thesis, we make the following contributions to address the above challenges.

1. We revisit three compiler optimizations (loop tiling and loop fusion for enhancing temporal locality and data prefetching for hiding memory latency) for improving memory (and parallel) performance in light of the various recent advances in microarchitecture, including deeper memory hierarchy, the multithreading technology, the (short-vector) SIMDization technology, and hardware prefetching, and propose generic algorithms implementable in production compilers for a range of processors.

- We propose wise heuristics in a cost model to choose good statements to fuse, and also improve dependence analysis to not loose critical fusion opportunity in application programs when it exists.

- 3. The final contribution of this thesis is a solution to the unscalability problem. Based on program semantics, we devise a way to represent the entire program with much fewer representative statements and dependences, leading to significantly improved compile time and memory requirement for compilation. Thus, real applications can now be optimized not only efficiently, but also at a very low overhead.

# Contents

| Ac             | Acknowledgements |                                                                              |    |  |  |

|----------------|------------------|------------------------------------------------------------------------------|----|--|--|

| De             | Dedication       |                                                                              |    |  |  |

| Al             | Abstract         |                                                                              |    |  |  |

| Li             | st of [          | fables                                                                       | ix |  |  |

| Li             | st of l          | Figures                                                                      | X  |  |  |

| 1 Introduction |                  | oduction                                                                     | 1  |  |  |

|                | 1.1              | Key challenges for compiler developers in the present day                    | 2  |  |  |

|                |                  | 1.1.1 The diverse world of computer architecture that also keeps on evolving | 2  |  |  |

|                |                  | 1.1.2 Real applications and poor show                                        | 5  |  |  |

|                |                  | 1.1.3 Unscalability: The traditional woe of compilers                        | 6  |  |  |

|                | 1.2              | Contribution of this thesis                                                  | 7  |  |  |

|                | 1.3              | Organization of the thesis                                                   | 8  |  |  |

|                | 1.4              | Related Publications                                                         | 9  |  |  |

| 2 Background   |                  | sground                                                                      | 10 |  |  |

|                | 2.1              | Loop Tiling and Tile Size Selection                                          | 11 |  |  |

|                | 2.2              | Data Prefetching                                                             | 13 |  |  |

|                | 2.3              | Loop Fusion and Polyhedral Compiler Framework                                | 15 |  |  |

|                |                  | 2.3.1 Overview of the Polyhedral Framework                                   | 16 |  |  |

| 3   | 3 Tile Size Selection, from Then to Now |                                                                          |    |  |

|-----|-----------------------------------------|--------------------------------------------------------------------------|----|--|

| 3.1 |                                         | Introduction                                                             | 20 |  |

|     | 3.2                                     | Motivation                                                               | 22 |  |

|     |                                         | 3.2.1 Modeling the effect of set-associativity                           | 22 |  |

|     |                                         | 3.2.2 Tapping into data reuse at multiple levels of cache                | 24 |  |

|     | 3.3                                     | Our Approach                                                             | 26 |  |

|     |                                         | 3.3.1 Data reuse in L1 cache                                             | 26 |  |

|     |                                         | 3.3.2 Data reuse in L2 cache                                             | 28 |  |

|     |                                         | 3.3.3 Data reuse in both L1 and L2 cache                                 | 29 |  |

|     |                                         | 3.3.4 Interaction with vectorization                                     | 31 |  |

|     |                                         | 3.3.5 Interaction with Time Skewing                                      | 32 |  |

|     |                                         | 3.3.6 Other factors that influence tiling                                | 34 |  |

|     | 3.4                                     | The Tile Size Selection (TSS) Algorithm                                  | 36 |  |

|     |                                         | 3.4.1 Scope of the algorithm                                             | 38 |  |

|     |                                         | 3.4.2 The Framework                                                      | 40 |  |

|     | 3.5                                     | Experimental Setup                                                       | 41 |  |

|     | 3.6                                     | Experimental Results                                                     | 42 |  |

|     | 3.7                                     | Related Work                                                             | 49 |  |

|     | 3.8                                     | Conclusion                                                               | 50 |  |

| 4   | Coo                                     | ordinated Multi-Stage Prefetching for Present-day Processors             | 52 |  |

|     | 4.1                                     | Introduction                                                             | 52 |  |

|     | 4.2                                     | Motivation                                                               | 55 |  |

|     | 4.3                                     | Coordinated Multi-stage Data Prefetching                                 |    |  |

|     |                                         | 4.3.1 What to Prefetch                                                   | 56 |  |

|     |                                         | 4.3.2 Where to Insert Prefetch Instructions                              | 57 |  |

|     |                                         | 4.3.3 When to Prefetch                                                   | 58 |  |

|     |                                         | 4.3.4 Multi-stage Prefetching in multi-threaded environment              | 62 |  |

|     | 4.4                                     | The Compiler Framework                                                   | 63 |  |

|     | 4.5                                     | Experimental Results and Discussion                                      |    |  |

|     |                                         | 4.5.1 Experimental Environment                                           | 65 |  |

|     |                                         | 4.5.2 Results for Multi-stage Prefetching in single-threaded environment | 66 |  |

|   |      |                                          | Results for Multi-stage Prefetching in multithreaded environment       | 73  |

|---|------|------------------------------------------|------------------------------------------------------------------------|-----|

|   | 4.6  | Relate                                   | d Work                                                                 | 74  |

|   | 4.7  | Conclu                                   | ision                                                                  | 76  |

| 5 | Loo  | op Fusion and Real Applications - Part 1 |                                                                        |     |

|   | 5.1  | Introdu                                  | action                                                                 | 77  |

|   | 5.2  | Motiva                                   | ation                                                                  | 79  |

|   |      | 5.2.1                                    | Why not scalar and array expansion (perhaps, followed by contraction)? | 81  |

|   |      | 5.2.2                                    | Why not scalar and array renaming across loop nests?                   | 82  |

|   | 5.3  | Backg                                    | round                                                                  | 83  |

|   |      | 5.3.1                                    | Some key concepts and definitions                                      | 84  |

|   | 5.4  | Our Aj                                   | pproach                                                                | 86  |

|   |      | 5.4.1                                    | Key Insight                                                            | 86  |

|   |      | 5.4.2                                    | Fusion of loop nests with same loop-order in the presence of temporary |     |

|   |      |                                          | array variables                                                        | 89  |

|   |      | 5.4.3                                    | Fusion of loop nests with different loop-orders                        | 89  |

|   |      | 5.4.4                                    | Cases in which dependence relaxation is not feasible                   | 90  |

|   | 5.5  | Impler                                   | nentation: putting it all together                                     | 91  |

|   |      | 5.5.1                                    | Validation of relaxation criteria                                      | 93  |

|   | 5.6  | Experi                                   | mental Evaluation                                                      | 94  |

|   |      | 5.6.1                                    | Setup                                                                  | 94  |

|   |      | 5.6.2                                    | Benchmarks                                                             | 94  |

|   |      | 5.6.3                                    | Results and Discussion                                                 | 95  |

|   | 5.7  | Relate                                   | d Work                                                                 | 100 |

|   | 5.8  | Conclu                                   | ision                                                                  | 102 |

| 6 | Loo] | p Fusio                                  | n and Real Applications - Part 2                                       | 103 |

|   | 6.1  | Introdu                                  | action and Motivation                                                  | 103 |

|   | 6.2  | Loop f                                   | Tusion and the polyhedral framework                                    | 107 |

|   |      | 6.2.1                                    | Existing fusion models in the polyhedral framework                     | 108 |

|   | 6.3  | Proble                                   | m Formulation                                                          | 109 |

|   | 6.4  | Our Fu                                   | sion Algorithm                                                         | 112 |

|   |      | 6.4.1                                    | Algorithm 3: Finding a good pre-fusion schedule                        | 112 |

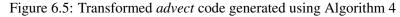

|   |            | 6.4.2   | Algorithm 4: Enabling Outer-level Parallelism                            | 116 |

|---|------------|---------|--------------------------------------------------------------------------|-----|

|   | 6.5        | Experi  | mental Evaluation                                                        | 118 |

|   |            | 6.5.1   | Setup                                                                    | 118 |

|   |            | 6.5.2   | Benchmarks                                                               | 119 |

|   |            | 6.5.3   | Results and Discussion                                                   | 120 |

|   | 6.6        | Relate  | d Work                                                                   | 124 |

|   | 6.7        | Conclu  | usion                                                                    | 126 |

| 7 | Add        | ressing | Scalability: Optimizing Large Programs at an Easy Price                  | 127 |

|   | 7.1        | Introdu | action                                                                   | 127 |

|   | 7.2        | Causes  | s of Unscalability                                                       | 131 |

|   |            | 7.2.1   | First Culprit: Phase I - Constructing legality constraints               | 131 |

|   |            | 7.2.2   | Second Culprit: Phase II - Using an ILP solver to find legal hyperplanes | 132 |

|   |            | 7.2.3   | Third Culprit: Phase III - Finding linearly independent hyperplanes      | 132 |

|   | 7.3        | Impler  | nentation                                                                | 134 |

|   | 7.4        | Experi  | mental Evaluation                                                        | 136 |

|   |            | 7.4.1   | Setup                                                                    | 136 |

|   |            | 7.4.2   | Benchmarks                                                               | 137 |

|   |            | 7.4.3   | Results and Discussion                                                   | 138 |

|   | 7.5        | Relate  | d Work                                                                   | 139 |

|   | 7.6        | Conclu  | usion                                                                    | 141 |

| 8 | Con        | clusion | and Discussion                                                           | 143 |

|   | 8.1        | Summ    | ary of important findings and directions for future research             | 143 |

|   | 8.2        | Final v | words                                                                    | 145 |

| 9 | References |         | 146                                                                      |     |

# **List of Tables**

| 3.1 | Details of the microarchitectures                                               | 41  |

|-----|---------------------------------------------------------------------------------|-----|

| 3.2 | Summary of the benchmarks                                                       | 41  |

| 3.3 | Comparison of the algorithms                                                    | 42  |

| 3.4 | Performance of TSS algorithm                                                    | 45  |

| 3.5 | Comparison between TSS and 'Copy and Tile'                                      | 48  |

| 3.6 | Performance of TSS algorithm in a multi-threaded environment                    | 49  |

| 4.1 | Summary of benchmarks with problem sizes.                                       | 65  |

| 4.2 | Details of the microarchitectures                                               | 66  |

| 4.3 | Summary of different prefetching strategies.                                    | 66  |

| 5.1 | Performance speedup of transformed program in Fig 5.1b and PLuTo generated code |     |

|     | (Fig 5.1c) wrt original code in Fig 5.1a                                        | 81  |

| 5.2 | Summary of fusion models in different compilers                                 | 94  |

| 5.3 | Summary of the benchmarks                                                       | 95  |

| 5.4 | Performance counters indicating reduced pipeline stalls and effective memory    |     |

|     | latency through <i>var-lib</i>                                                  | 98  |

| 5.5 | Compile time, memory requirement of different compilers and overall (applica-   |     |

|     | tion) speedup (S) achieved by <i>var-lib</i> over <i>ifort</i>                  | 98  |

| 6.1 | Summary of the fusion models                                                    | 118 |

| 6.2 | Summary of the benchmarks                                                       | 119 |

| 7.1 | Summary of the benchmarks                                                       | 137 |

| 7.2 | Compile time, memory requirement of different compilers                         | 139 |

| 7.3 | Compile times for the three time consuming phases in polyhedral compilation .   | 139 |

# **List of Figures**

| 2.1 | Matmul - untiled (left) and tiled (right)                                                             | 11 |

|-----|-------------------------------------------------------------------------------------------------------|----|

| 2.2 | (a) Demonstration of self-interference ( $ld_B = 512$ ); (b) Demonstration of cross-                  |    |

|     | interference $(ld_A = ld_B = 2000)$ ; $[ld_A \text{ and } ld_B \text{ are leading dimensions of}]$    |    |

|     | arrays A and B, respectively]                                                                         | 13 |

| 2.3 | Loop fusion                                                                                           | 15 |

| 2.4 | Overview of the Polyhedral Framework                                                                  | 17 |

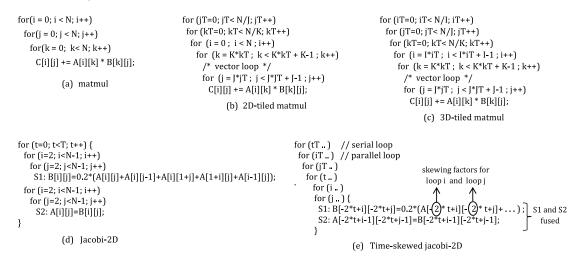

| 3.1 | Source codes of <i>matmul</i> and <i>jacobi-2d</i> , before and after tiling through PLuTo .          | 23 |

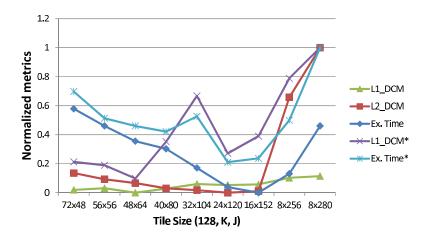

| 3.2 | Normalized metrics for <i>matmul</i> (N=2000); L1 size = $32KB$ ; L2 size = $256KB$ .                 | 24 |

| 3.3 | Choosing a tile size that exploits data reuse in both L1 and L2 cache $\ldots$ .                      | 30 |

| 3.4 | Vectorization, reuse and tile size                                                                    | 32 |

| 3.5 | Illustration of skewed-tile traversal                                                                 | 33 |

| 3.6 | Our Framework                                                                                         | 40 |

| 3.7 | Comparison of TSS with other approaches that use 3D-tiling                                            | 46 |

| 4.1 | An example loop nest in the <i>swim</i> benchmark                                                     | 55 |

| 4.2 | The <i>matmul</i> kernel                                                                              | 57 |

| 4.3 | (a) Tiled <i>matmul</i> ; (b) Tiled <i>matmul</i> with prefetching as in the <i>general</i> case; (c) |    |

|     | Tiled <i>matmul</i> with prefetching as in the <i>special</i> case                                    | 61 |

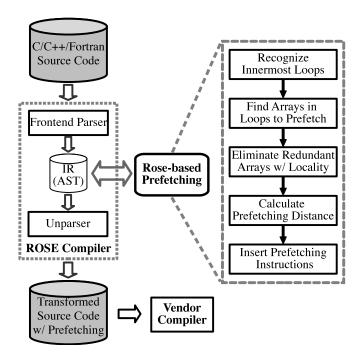

| 4.4 | Compiler framework for coordinated multi-stage prefetching                                            | 64 |

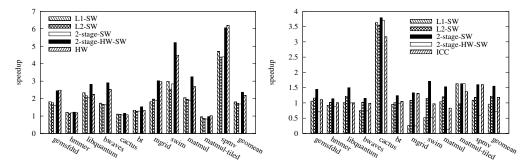

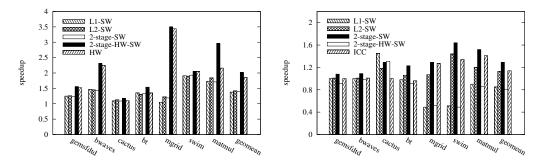

| 4.5 | Performance speedup of different prefetching strategies on single thread in (a)                       |    |

|     | SandyBridge (results normalized wrt baseline pref.) (b) Xeon Phi (results nor-                        |    |

|     | malized wrt hardware pref.)                                                                           | 67 |

| 4.6 | An example loop nest with prefetching instructions to L1 and L2 cache in the                          |    |

|     | libquantum benchmark                                                                                  | 70 |

| 4.7 | Sparse matrix-vector multiplication with prefetching instructions to L1 and L2 cache.       | 71  |

|-----|---------------------------------------------------------------------------------------------|-----|

| 4.8 | Performance speedup of different prefetching strategies using CMP technique                 |     |

|     | in (a) SandyBridge (results normalized wrt baseline pref.) (b) Xeon Phi (results            |     |

|     | normalized wrt hardware pref.)                                                              | 73  |

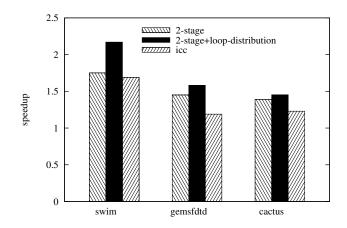

| 4.9 | Performance speedup with loop distribution in Xeon Phi (results normalized wrt              |     |

|     | hardware pref.)                                                                             | 74  |

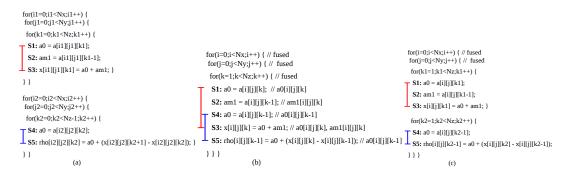

| 5.1 | (a) Original code, (b) Optimized (or transformed) code, and (c) Transformed program         |     |

|     | generated by PLuTo                                                                          | 80  |

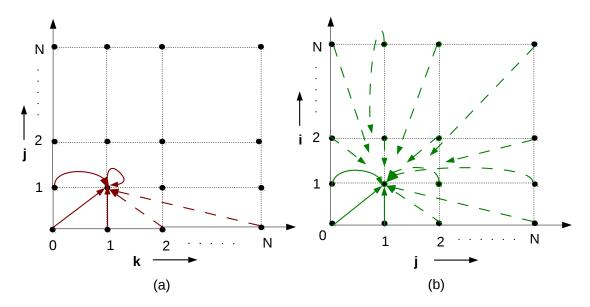

| 5.2 | Instancewise (RAW) dependence between statements (a) S1 and S2, and (b) S2 and S8;          |     |

|     | the dashed arrows in the figure indicate a backward (RAW) dependence                        | 83  |

| 5.3 | Live range interference                                                                     | 86  |

| 5.4 | (a) Example program, (b) (Incorrectly) Transformed program after dependence relax-          |     |

|     | ation, and (c) Correctly transformed program                                                | 86  |

| 5.5 | (a) Loop nests with different loop-orders, (b) Loop fusion after interchange and liber-     |     |

|     | alization                                                                                   | 89  |

| 5.6 | Example programs where dependence relaxation is infeasible                                  | 91  |

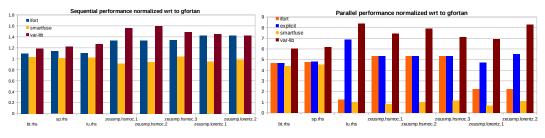

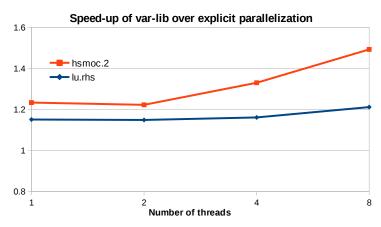

| 5.7 | Performance results using (a) single thread (b) 8 threads (cores)                           | 95  |

| 5.8 | Parallel performance comparison of var-lib and explicit parallelization for rhs             |     |

|     | subroutine in lu                                                                            | 97  |

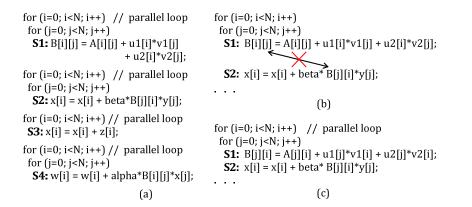

| 6.1 | (a) the gemver kernel; (b) illegal fusion; (c) legal fusion after loop interchange          |     |

|     | in the first loop-nest;                                                                     | 104 |

| 6.2 | the <i>swim</i> benchmark                                                                   | 105 |

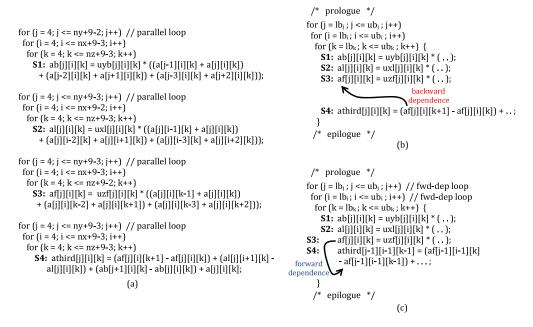

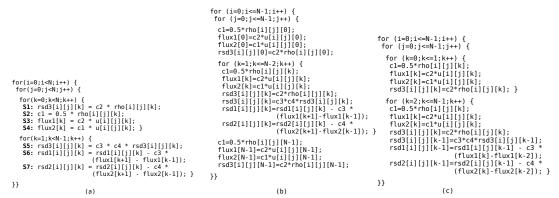

| 6.3 | (a) Original source code for <i>advect</i> ; (b) Fully fused <i>advect</i> without shifting |     |

|     | (incorrect code); (c) Fully fused <i>advect</i> with shifting (correct code)                | 111 |

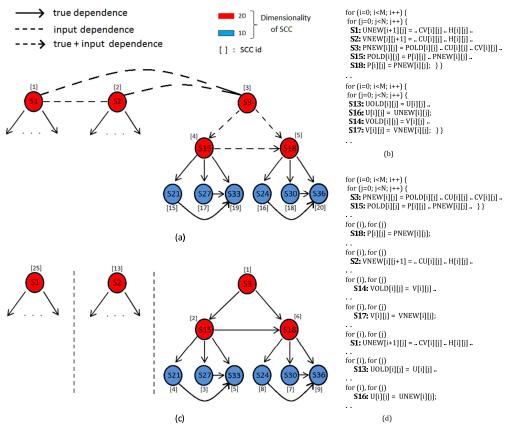

| 6.4 | Our fusion model: (a) Partial DDG for <i>swim</i> and pre-fusion schedule from Al-          |     |

|     | gorithm 3; (b) Fused code corresponding to (a); (c) Pre-fusion schedule chosen              |     |

|     | by PLuTo; (d) Fused code corresponding to (c)                                               | 113 |

| 6.5 | Transformed <i>advect</i> code generated using Algorithm 4                                  | 118 |

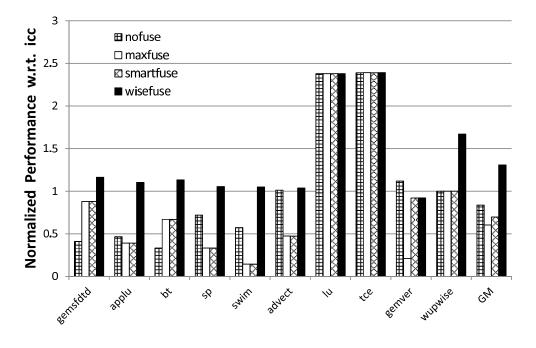

| 6.6 | Results                                                                                     | 120 |

| 6.7 | Partitioning achieved by different fusion models for the gemsfdtd benchmark                 |     |

|     | (values in each column are spaced out for readability)                                      | 121 |

| 7.1 | (a) Original program; (b) Representative program with condensed set of statements and   |     |

|-----|-----------------------------------------------------------------------------------------|-----|

|     | dependences                                                                             | 128 |

| 7.2 | (a) Original program; (b) Incorrectly transformed (fused) program; (c) Correctly Trans- |     |

|     | formed program (with shifting in S5-S7)                                                 | 136 |

## **Chapter 1**

# Introduction

Until a decade ago, Moore's law translated into deeper pipelines (and corresponding increase in processor frequency), sophisticated cores with newer technologies for branch prediction and Instruction-level Parallelism (ILP), and larger on-chip caches. All this meant increasing performance gains without any involvement of the programmer or the optimizing compiler. However, this trend has changed for various reasons. It is now no longer possible to increase the clock frequency due to power dissipation issues (1). The era of ILP has also witnessed an end since very little gains from employing transistors for extracting ILP are estimated, and the community has exhausted options in this regard (2). The combined effect has been a shift to *multiple cores* on a chip, where each core runs at a lower frequency to save power. Since the number of transistors can now be increased in accord with Moore's law without excessive power consumption, continued increase in performance can be sustained. This performance increase is, however, contingent on ability of the source program to tap into the parallelism exposed by the hardware.

This marked shift in the processor design has brought about a renewed focus on compiler design. Earlier, the onus of improving performance was borne mostly by the hardware without a significant contribution by the compiler or the programmer. This was natural since performance improvement could be achieved by optimizing execution of instructions within a small window through techniques for extracting ILP. These techniques included dynamic out-of-order execution, superscalar processing, speculative execution and non-blocking caches. However, with the introduction of multi-core processors, extracting parallelism from within a few instructions is not sufficient, and parallelism at a much more coarser level is necessitated. This coarse-grained parallelism is not easy for the hardware to extract since it has a view of a narrow window of

instructions. Therefore, the onus of improving performance on multi-core processors has to be now borne by either the compiler or the programmer.

Clearly, extracting coarse-grained parallelism where the compiler directs each core on the host hardware to execute specific portions of the source program, is certainly one important responsibility of the compiler. However, the shift to multicore has also had other important implications which cannot be ignored. In particular, when multiple cores on the chip compute in parallel, they also consume data in parallel. This implies simultaneous requests for data from the off-chip memory. Now, it is well known that the improvement in memory speed has not kept up pace with the processor speed (leading to the memory wall), and multiple cores on chip only help to accentuate this gap between the processor and memory. Another related effect that creeps in and is equally harmful to performance is the bandwidth wall, where effective memory latencies increase due to bandwidth contention resulting from memory-intensive applications and poor memory performance. Thus, alleviating effects of memory wall and bandwidth wall for multi-cores is the second important responsibility of the parallelizing compilers. Again, like parallelization, the hardware cannot excavate opportunties existent in the source programs for any potential improvements in memory performance. It is certainly unrealistic to pass this responsibility to the programmer, because the host platforms tend to be so different and evolving, and NOT all programmers like to be 'close to the silicon' or feel comfortable at reasoning an optimization for long sequences of loop nests at their disposal. In such a scenario, traditional memory optimizations such as loop tiling, loop fusion, and data prefetching performed by a parallelizing compiler assume renewed significance.

### 1.1 Key challenges for compiler developers in the present day

While the two important responsibilities of a parallelizing compiler are well understood, it is also important to understand the challenges facing the compiler developers when meeting these resposibilities. Our experience with parallelizing compilers and present-day architectures reveals that there are three key challenges in this regard:

#### **1.1.1** The diverse world of computer architecture that also keeps on evolving

The first key challenge in developing a compiler stems from its intimate relationship with the host hardware. For any compiler to yield the best performance when applying a particular optimization, it must have a thorough understanding of the host hardware. For example, the choice of a good tile size depends on the size of the cache, its set-associativity, number of levels of

cache, prefetching behavior of the hardware, etc. Similarly, the degree of aggressiveness at which loops should be fused, depends on cache characteristics, vectorization potential of the host hardware, etc. As a result, it becomes difficult for a compiler to perform optimally on the diverse set of microprocessors that exist today. While the characteristics of the contemporary microprocessors from different vendors such as AMD and Intel are largely the same, we identify that an even more important problem is that traditional compiler optimizations such as loop tiling, loop fusion and prefetching as they exist in present-day processors have failed to evolve with the major changes to computer microarchitecture in the last decade (over multiple microarchitecture generations). The changes include the following:

- 1. Deep memory hierarchies Having recognized the importance of alleviating off-chip memory accesses, the existing multi-cores have seen a shift from single-level, to two-level, to now a three-level cache hierarchy. However, important compiler optimizations such as loop tiling as they exist in current production compilers do not account for this change. Most of the work on loop tiling assumes that processors need to achieve data reuse in a single level of cache, and there is some work that assumes a two-level cache hierarchy, but the optimization is still not tuned for optimal reuse. Similarly, existence of multiple levels of cache and the opportunity to prefetch data selectively to those levels requires a carefully executed strategy for optimal performance in current processors, perhaps with coordination between the compiler and hardware.

- 2. The multithreading technology In current processors, multithreading is available through either Chip Muti-Processing (CMP) or Simultaneous Multi-Threading (SMT). Both these technologies have a bearing on the memory optimizations performed by the compiler. For example, if 2 threads are running in CMP, then the two threads simultaneously bring the data to the shared last level cache. Similarly, if 2 threads are running in SMT, then they bring in data simultaneously to even the private L1 or L2 cache on each core, and thus reduce each other's share of the cache. Threads in SMT may have an even more involved relationship. For example, in Intel's latest many-core processor, Xeon Phi, a thread can only issue instructions once every 2 cycles, and another thread is granted opportunity for the next cycle. In such cases, the compiler must account for such behavior for optimal performance.

- 3. The vectorization technology Current processors employ efficient vectorization or

SIMD (Single-Instruction Multiple Data) units to perform parallel computation (called vectorization) on short vectors. The vectorization technology is used to extract the second level of parallelization available in source program which is at a much finer-granularity (generally the innermost loop in a loop-nest) than the coarse-grain or outer-loop parallelism. Current production compilers, particularly the Intel compiler, are adept at finding vectorizable loops because vectorization purchases considerable performance improvement. We recognize that although production compilers are not so good in finding coarsegrain parallelism, they can find fine-grain parallelism because the analysis merely involves a single loop and its body, instead of an entire loop-nest. However, they still fail to study its interaction with other memory optimizations such as loop tiling and loop fusion. For example, if the compiler takes the approach of aggressive loop fusion, then that might hurt vectorization because of introduction of loop-carried dependences in the innermost loop. Similarly, certain tile sizes benefit significantly more from vectorization than others, and thus vectorization has an important say in tile size selection as well. In some cases, tiling may even degrade performance of the source program because of its detrimental impact on vectorization.

4. The prefetching technology - Data prefetching is the single most important and generally applicable technology that fetches performance on existing multi- and many-core processors. This is because the gap between the processor and the memory speed is the largest in the present day, and it is therefore required to pre-fetch the data from the slow memory for timely execution. The way this technology interacts with the compiler is that the compiler is also armed with prefetch instructions, and thus software and hardware prefetching contend with each other. To add to this, there are hardware prefetchers for different levels of cache, and so are there software prefetch requests for different levels, and to decide how they should coordinate to achieve the best performance is a live challenge. Certainly, the compiler cannot perform the prefetching optimization oblivious of the hardware prefetcher's abilities and inabilities. It should instead know those and complement the weaknesses of the hardware prefetcher. Also, since prefetching is so crucial to performance, other optimizations such as tiling and fusion must be performed by the compiler so as to not hurt prefetching. For example, tiling induces block-wise execution of the program arrays instead of sequential execution. This hurts prefetching, and thus requires a careful balance. Similarly, aggressive fusion may result in merging many arrays

into the same nest. This increases the number of prefetch streams required to monitor them, and the processor may fall short of them which can potentially hurt performance.

Since such an intimate interaction exists between compiler memory optimizations and the above-mentioned important advances in computer microarchitecture, it is important for the compiler to take into account the host hardware features for best performance. We suggest that the compiler should ideally extract this needed information from the processor's host OS or during its installation, and then use it every time it goes ahead to perform its optimizations. In any case, these optimizations need to be implemented in a compiler in a way that it provides the needed flexibility to adapt to different hosts.

#### **1.1.2** Real applications and poor show

The greatest times of need for a programmer are when the source code is large and requires memory optimizations to improve performance. Such is the case in many real scientific applications, and the compiler's help is inevitably sought. However, our experiments with the state-of-the-art production compilers on such real applications from popular benchmark suites, show that it is in such cases, that the compiler is particularly ineffective. Although there exists immense opportunity to improve temporal locality of data accessed in such applications, the compiler is actually able to do very little to help the programmer in need. We identify that this unfriendliness of the compiler in such circumstances arises from 2 key reasons:

1. The hot subroutines in various scientific applications contain sequences of loop nests. These loop nests tend to access common data and thus contain substantial opportunity for data reuse through fusion. However, the production compilers either simply choose to ignore the possibility of fusion, or choose to be very restrictive in fusing nests. The first important reason is that they only consider very small scopes for fusion, such as just consecutive nests in 'pair-wise fusion'. Thus, if two nests that are not adjacent are fusable, the compiler will simply ignore the possibility. This is a consequence of the compiler's view of reducing analysis time by deciding on small scopes and thus fewer dependences to analyze. Also, the criteria to be chosen for deciding the best fusion structure is unclear especially in the wake of recent changes to microarchitecture as discussed above. For example, if the compiler leads to an imperfect fusion of nests (which results when the fused nests have different loop-depth) with the help of the insertion of conditional clauses in

the loop body, then it could hurt vectorization, and be unprofitable. Thus, a clear criteria or more precisely, a cost model, is necessitated to decide on good fusion structures.

2. The second important problem is that even if the criteria for choosing nests to fuse is decided, the fusion is hindered by the occurrence of certain artificial dependences between the candidate nests due to the frequent use of temporary variables in such large scientific applications. The use of such temporary variables, both scalars and arrays, arises from the fact that these applications compute partial results to be immediately used in the program. Those partial results are stored in temporary variables to avoid re-computation. Existing production compilers, because of their oversight of the importance and opportunity of fusion in such applications, tend to ignore the presence of such fusion-preventing dependences. These dependences are artificial because they can be safely relaxed if certain criteria are fulfilled, in which case they no longer remain fusion-preventing.

Thus, it is important for the compiler to address these weaknesses to be a 'friend in deed' of the programmer.

#### **1.1.3 Unscalability: The traditional woe of compilers**

The third and the most important reason for the poor performance of current production compilers especially for large programs is their own choice in doing so. This choice, is however, forced, because they need to maintain programmer productivity through short compile times. That is, the compilers choose to not consider global program optimizations (or optimizations spanning a large scope of statements) so as to circumvent the issue of analyzing a large number of dependences for reasoning the application of a certain optimization such as fusing multiple loop nests. In short, the compiler's capability of performing useful optimizations does not scale to large programs.

Traditionally, large compile times have been associated with analyzing (many) dependences in a large program to generate the Program Dependence Graph (PDG). The PDG is then used to reason optimizations such as parallelization, fusion, distribution, etc. However, our experiments with a state-of-the-art polyhedral compiler that is armed with the capability of analyzing large scopes and performing useful global optimizations, reveal that the unscalability of compilers is more a problem when applying useful optimizations than just analyzing dependences to build the PDG. For example, it takes less than a second to analyze dependences and construct the PDG in a scientific application, *lu*, whereas effectively optimizing it takes around 3 hours. We are not aware of an existing work that attempts to tackle this important problem, and this problem is in fact, now well recognized in the polyhedral compiler community as a key challenge.

### **1.2** Contribution of this thesis

This thesis makes contributions to address all three above-mentioned challenges involved in designing parallelizing compilers. In addition to parallelism, we focus on three key compiler optimizations to improve the memory system performance of applications, which in effect amounts to parallel performance. The three optimizations are loop tiling, loop fusion and data prefetching. Through our work on these three optimizations, we address all three challenges as follows.

- 1. We look at memory optimizations in light of the present-day processors that contain the recent advances in microarchitecture such as multi-level caches, multithreading, vectorization, prefetching. In particular, we revisit the locality enhancing optimization, loop tiling, such that interference misses in caches that stem from the caches being set-associative instead of fully-associative, are minimized, and the chosen tile size best benefits from vectorization and prefetching. Its interaction with multi-threading is also considered, and a generic algorithm that takes these parameters as input is presented, which can thus find utility in any compiler on any host. Similarly, the latency hiding optimization, data prefetching, is visited in light of the hardware supporting prefetching in current processors, a multi-level cache hierarchy, and also multithreading. The decision on the aggressiveness of loop fusion is also made based on cache sizes and maximizing benefits of vectorization. Experimental results indicate significant performance gains over the production compilers on existing multi- and many-core processors when considering the important recent advances in microarchitecture.

- 2. The solution to the challenge of optimizing large programs includes, (1) relaxing the extra-stringent fusion preventing dependences between temporary variables across loop nests so as to enable effective fusion while also preserving program correctness in the wake of relaxed dependences, and (2) implementing an effective cost model that chooses wise heuristics to decide the statements to be fused to achieve global data reuse; the fusion achieved is such that it does not hurt coarse-grain parallelism. This work is implemented in the state-of-the-art PLuTo polyhedral compiler and has been shown to provide parallel performance improvement of as much 2.17x for individual applications, and as much as

6.8x over the Intel compiler for individual hot regions in those applications when run on an 8-core Intel Xeon processor.

3. The unscalability problem at its very root stems from the large number of program statements and dependences within hot regions in real application programs. The algorithms employed for the purpose of computing transformations have a time and memory complexity that varies as a large power in the number of statements, and thus become unscalable. We address this problem with a one-shot solution - condense the program (or hot region) to be represented by a semantically equivalent but smaller set of statements and dependences. Essentially, we choose a single representative statement in an entire loop, which we call an *Optimization-molecule*. This condensation also then helps us to condense the set of program dependences. With this condensation, global program transformations such as loop fusion (and its supporting transformations such as interchange and shifting) can still be effectively reasoned, and that too, at a much lower overhead. Experimental results indicate significant improvement in compile time and memory requirement for program subroutines with more than 100 statements.

### **1.3** Organization of the thesis

In the following chapters of this thesis, each compiler optimization is dealt separately with the focus on addressing the above-identified 3 challenges for parallelizing compilers. Chapter 2 provides the background for the thesis - it introduces the three compiler optimizations that are dealt in this work and particularly provides a gentle introduction to the polyhedral compiler framework. Chapter 3 discusses loop tiling and tile size selection for present-day processors, clearly showing the impact of hardware on this optimization and then our solution to account for all of them in a neat algorithm. Chapter 4 discusses data prefetching as an important latency hiding optimization for both the latest multi-core and the many-core processors. This chapter shows how the optimal prefetching strategy on each platform is clearly a function of the host platform and is widely different on these two platforms. Particularly, the best performing strategy on one is the worst on the other and vice-versa. On each platform, we propose an algorithm for the compiler to selectively prefetch data using carefully tuned prefetch distance at different levels of cache, and also coordinate with the existing hardware prefetcher on the host platform when helpful. Chapters 5 through 7 deal with global program optimizations, particularly loop fusion for real application programs. Chapter 5 presents our solution to relaxation of dependences on

temporary variables across loop nests to enable effective loop fusion in large programs. Chapter 6 complements Chapter 5 by providing an effective cost model to decide what statements should be fused to benefit most from data reuse while preserving parallelism. Chapter 7 nicely closes this discussion by addressing a long-standing problem in compilers - scalability. Thus, finally, real applications can be effectively optimized for locality and parallelism, and that too, at a cheap price in terms of time and memory. Finally, we present the conclusions from our work in Chapter 8.

### **1.4 Related Publications**

Portions of the work presented in this thesis have been published in the form of three papers. They are as follows.

- Sanyam Mehta, Gautham Beeraka and Pen-Chung Yew. Tile Size Selection Revisited. In ACM Transactions on Architecture and Code Optimization, 10, 4, Article 35 (December 2013), 27 pages.

- Sanyam Mehta, Pei-Hung Lin and Pen-Chung Yew. Revisiting Loop Fusion in the Polyhedral Framework. In Proceedings of the 19th ACM SIGPLAN symposium of Principles and Practice of Parallel Programming (PPoPP '14). ACM, 233-246.

- Sanyam Mehta, Zhenman Fang, Antonia Zhai and Pen-Chung Yew. Multi-stage Coordinated Prefetching for Present-day Processors. In Proceedings of the 28th ACM International Conference on Supercomputing (ICS '14). ACM, 73-82.

## **Chapter 2**

# Background

Traditionally, compiler optimizations for improving the memory performance of a processor have been broadly categorized into, (1) *locality enhancing*, and (2) *latency hiding* optimizations.

Many application programs involve multiple updates (writes) to the same data in the form of arrays, lists, etc. Such programs thus *reuse* data. However, the program may be written in a way that it cannot reuse the data in a faster level of memory hierarchy due to its limited size. Thus, *locality enhancing* optimizations transform the program to allow such data reuse. This prevents incurring costly off-chip memory accesses, and also reduces the use of off-chip bandwidth, both amounting to improved performance. *Loop tiling* and *loop fusion* are the two most prominent *locality enhancing* compiler optimizations.

In other applications, there may not be much opportunity to reuse data, or at least the compiler may not be capable of automatically transforming the program to extract such reuse. In such cases, an application (particularly if it is memory intensive as is the case with most scientific applications) could suffer performance loss due to waiting for data to arrive from memory. In such cases, *data prefetching* as a *latency hiding* optimization comes to the rescue. In this optimization, the compiler identifies the data needed in the immediate future, and pro-actively requests for it, so that the execution can proceed unimpeded without suffering from memory latency. Thus, *data prefetching* makes for the slow memory speed, and boosts program performance.

In the rest of this chapter, we provide more specific background for each of these three optimizations. In particular, loop fusion and the polyhedral compiler framework are discussed in more detail.

Figure 2.1: Matmul - untiled (left) and tiled (right)

### 2.1 Loop Tiling and Tile Size Selection

Loop tiling converts a program that originally involves sequential traversal of the data (in arrays) to data traversal in tiles. This reduces the amount of data accessed between consecutive accesses to the same (i.e. reusable) data, and thus promotes data reuse in faster and smaller levels of the memory hierarchy such as caches.

Figure 2.1 shows the original *matmul* (matrix-multiplication) kernel and also its tiled version. The 3 loops in the original code become 6 loops, 3 of which traverse the data within the tile and are called the intra-tile loops, and the remaining 3 loops iterate between tiles and are called the inter-tile loops. In the figure, the loops (iT-jT-kT) in the tiled program are the inter-tile loops, and loop (i-j-k) are the intra-tile loops. To aid the understanding of our work on tile size selection in relation to loop tiling, it is important to understand the following concepts/definitions.

There are 2 types of data reuse that are especially relevant to tile size selection:

Self-temporal reuse. This happens when the same reference reuses a data item in distinct loop iterations. For example, the array reference B[k][j] in the tiled *matmul* kernel in Figure 2.1 reuses the same data items in every iteration of loop i, and thus can be said to have *self-temporal reuse* in loop i. Similarly, array references A[i][k] and C[i][j] have self-temporal reuse in loops j and k, respectively. However, array reference B[k][j] reuses an entire tile in each iteration of the outermost loop i, array reference C[i][j] reuses a tile-row in each iteration of loop k, and the array reference A[i][k] reuses only an element in each iteration of loop j.

Thus, only array references with self-temporal reuse in the outermost loop such as B[k][j] provide opportunity for considerable data reuse. It is only in the presence of such references in

11

the source code that loop tiling gives a significant benefit. Thus, it is important to track such references and focus on minimizing conflict misses caused by such references.

Self-spatial reuse. This happens when a reference reuses the same cache line in distinct loop iterations. For example, the array references C[i][j], A[i][k] and B[k][j] in the tiled *matmul* kernel in Figure 2.1 all reuse same cache lines for multiple successive iterations of loops j, k and j, respectively, and can be thus said to have *self-spatial reuse* in the respective dimensions. It is for this reason that self-spatial reuse is best availed when the tile dimensions are a multiple of the cache line size.

Data reuse is enabled by data locality, i.e. data is reused if the data is not replaced from the cache before subsequent use. Thus, corresponding to the 2 types of data reuse, there are 2 types of data locality, i.e. *self-temporal* and *self-spatial* locality. Loop tiling improves the self-temporal locality of data by reducing its reuse distance. Since the reuse distance is a function of the tile size, tile size should be chosen such that data items accessed within a tile are not replaced from the cache due to capacity or conflict misses.

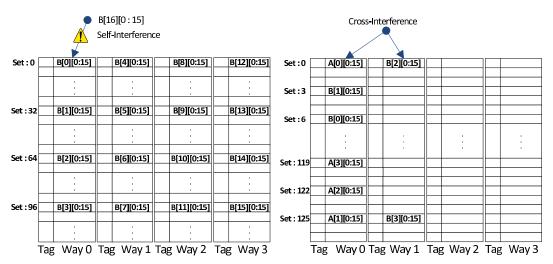

In the tiled code, capacity misses can be easily avoided by choosing a tile whose working set size is smaller than the cache capacity. This, however, doesn't avoid conflict misses that result from non-contiguous memory accesses within the tile. The conflict (or interference) misses are of 2 types - *self* and *cross interference* misses. Self interference misses occur when a reference with self-temporal reuse accesses multiple data items that collide in the cache, i.e. they are mapped to the same set. For example, in tiled *matmul*, self-interference occurs when data items accessed by the reference B[k][j] collide. This is demonstrated in Figure 2.2a which shows the snapshot of a 32KB 4-way set associative L1 cache with 16-element cache lines, at the instance when self-interference begins to cause misses during the execution of an array tile. Self-interference is pronounced for problem sizes<sup>1</sup> that are a power of 2. This is because the cache size is also a power of 2. In such a case, different rows in the tile are prone to map to the same set. This is seen in Figure 2.2a where the leading dimension of array B  $(ld_B)$  is 512 - the  $17^{th}$  row of the tile interferes with the first row of the tile. Thus, for the given cache configuration and problem size, the tile height, or number of rows in the tile, should not exceed 16 or else conflict misses will result. In this example, the tile width was chosen to be 16, the size of the cache line, but the case of pronounced conflict misses depends primarily on the tile

<sup>&</sup>lt;sup>1</sup>Problem size refers to the size of the array or matrix in a program. However, in this chapter, we mention problem size to particularly refer to the *leading dimension* of the array, which is critical for tile size selection. For row-major 2D arrays as in C, elements from one row to the next are a *leading dimension* apart.

height.

Cross interference misses occur when two or more references collide in the cache and one of them has self-temporal reuse. For example, in the tiled *matmul* kernel, cross-interference occurs when data items accessed by the references to arrays A, B and C collide. Figure 2.2b shows a snapshot of the cache demonstrating cross interference between references to arrays A and B, where the leading dimension of the arrays is 2000. In the figure, we assume that references A[0][0] and B[0][0] map to sets 0 and 6, respectively. However, run-time addresses of the arrays are not known at compile-time and thus cross interference is harder to account for. Among works based on an analytical model, (3) and (4) have attempted to minimize cross-interference misses, but only for direct-mapped caches.

Figure 2.2: (a) Demonstration of self-interference  $(ld_B = 512)$ ; (b) Demonstration of crossinterference  $(ld_A = ld_B = 2000)$ ;  $[ld_A$  and  $ld_B$  are leading dimensions of arrays A and B, respectively]

### 2.2 Data Prefetching

Data prefetching involves detection of specific access patterns in the executing program and leveraging it to issue requests for data to be accessed in the future to hide the latency of data access. For example, for the (untiled) *matmul* kernel shown in Figure 2.1, we see that consecutive elements of array A will be referenced since loop k is the innermost loop, and it corresponds to its fastest running subscript. Thus, future data needed by such a reference is easily predicted,

and prefetched for performance improvement. However, *matmul* is not particularly memory intensive due to available reuse, and thus benefits more from tiling. But, not all applications have such inherent reuse. Over the years, data prefetching has proved to be very useful for memory intensive applications, and thus both hardware and software techniques exist to detect access patterns and thereby issue prefetch requests.

In *hardware-based prefetching*, some special hardware monitors data access patterns to a particular cache and identifies data suitable for prefetching based on obtained information. Current processors employ multiple hardware prefetchers for *streaming* as well as *strided* accesses.

*Software-directed prefetching*, on the other hand, involves the insertion of prefetch instructions into the original code by the programmer or the compiler that request data needed a few iterations later. This distance in the number of loop iterations is called the *prefetch distance*. Like hardware prefetchers that sit on multiple levels of cache and can prefetch data to those levels, the latest instruction sets provide prefetch intrinsics for prefetching data at different levels of cache.

In software-directed prefetching, it is the responsibility of the programmer to ensure timeliness and prevent redundant prefetches by deciding the data to prefetch and the prefetch distance. The hardware prefetchers usually ensure timeliness through aggressive prefetching, i.e. maintaining a prefetch degree of more than one. For example, the streamer hardware prefetchers on SandyBridge (a multi-core processor) and Xeon Phi (a many-core processor) have prefetch degrees of 2 and 4, respectively, and can maintain a prefetch distance of a maximum of 20 cache lines. Depending on implementation, software prefetch instructions can also be used to train and thus control the prefetch distance at which the hardware prefetcher operates. *Comparing software-directed and hardware-based prefetching, software-directed prefetching has the advantage of being used in a controlled manner, but is associated with an additional instruction overhead which may compete with the gains.*

While the above-mentioned facts about prefetching are better known, the impact of other hardware features influencing prefetching are less well understood. We brief this interaction between hardware features and prefetching here to help the understanding of our strategy of coordinated prefetching in Chapter 4. The hardware tracks the outstanding prefetch requests through a buffer or a queue. This hardware structure is called the *Line Fill Buffer* (LFB) in SandyBridge and MSHR (*Miss Status Handling Registers*) file in Xeon Phi, and is responsible for rendering the data prefetch requests *non-blocking*. The size of the LFB or the MSHR file,

```

for i = 1 to N

a[i] = b[i] + c[i];

for i = 1 to N

d[i] = a[i] + e[i];

for i = 1 to N

Loop fusion

for i = 1 to N

a[i] = b[i] + c[i];

d[i] = a[i] + e[i];

```

Figure 2.3: Loop fusion

among other factors, has a significant bearing on the most appropriate choice of prefetching strategy on a particular architecture. This is because, on Xeon Phi, if the MSHR file is full, the pipeline stalls. On SandyBridge, if the LFB is full, subsequent prefetches/loads enter the load buffer, which when full, stalls the pipeline. Thus, any prefetching strategy must issue prefetch requests in such a way that it leads to minimum contention for this scarce resource - the LFB or the MSHR file.

### 2.3 Loop Fusion and Polyhedral Compiler Framework

Loop fusion groups references to the same data by merging the loop bodies of multiple loop nests into the same nest. For example, in Figure 2.3, the array a is referenced in two different loop nests which leads to access to similar data in both nests. In the fused program, the two references are grouped into the same nest. As a result, the successive uses of the same data (of array a) happen in the same iteration of loop i, as compared to the original program, when such accesses were separated by N loop iterations. This improved temporal locality of data reduces the costly accesses to off-chip memory, amounting to improved performance.

In this dissertation, we implement loop fusion within the polyhedral compiler framework, and use our framework to then address loop fusion in real applications. Thus, we next provide a gentle introduction to the polyhedral framework with particular emphasis on aspects relevant to our work in this thesis. The reader is referred to existing literature (5; 6; 7) for more detail on polyhedral compiler frameworks.

DEFINITION 1 (Affine Hyperplane). An affine hyperplane is an n - 1 dimensional affine sub-space of an n dimensional space. An affine hyperplane can be viewed as a one-dimensional affine function that maps an n-dimensional space onto a one-dimensional space, or partitions an n-dimensional space into n-1 dimensional slices. Hence, as a function, it can be written as,  $\Phi(\vec{v}) = h.\vec{v} + c$ . A hyperplane divides the space into two half-spaces, the positive half-space, and a negative half space. DEFINITION 2 (Polyhedron). A polyhedron is an intersection of a finite number of halfspaces. A polytope is a bounded polyhedron.

LEMMA 1 (Affine form of the Farkas lemma). If a non-empty polyhedron is defined by p inequalities or faces,

$$\mathbf{a_k}\vec{x} + b_k \ge 0, k = 1, p \tag{2.1}$$

then, an affine form  $\psi$  is non-negative everywhere in that polyhedron iff it is a non-negative linear combination of the faces:

$$\psi(\vec{x}) \equiv \lambda_0 + \sum_{k=1}^p \lambda_k (\mathbf{a_k} \vec{x} + b_k), \lambda_0, \lambda_1, \dots, \lambda_p \ge 0$$

(2.2)

#### 2.3.1 Overview of the Polyhedral Framework

The polyhedral framework for compiler optimizations is a powerful mathematical framework based on parametric linear algebra and integer linear programming. It provides an effective intermediate representation that captures nearly all the complex high level optimizations performed by a traditional automatic parallelizing compiler.

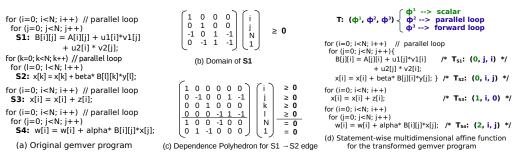

The polyhedral framework performs loop transformations on a *Static Control Part* (SCoP), a maximal set of consecutive statements  $(S_1, S_2, ..., S_n)$ , where loop bounds and conditionals are affine functions of the surrounding loop iterators and parameters. The *iteration domain* of the statements within a SCoP can be specified as a set of linear inequalities in the polyhedral framework as shown in Figure 2.4b. This set of linear inequalities defines a polyhedron, with each iteration of a loop represented by an integer point within this polyhedron. With such an abstraction, it is possible not only to obtain the exact dependences between statements, but also to model a composition of complex transformations as a single algebraic operation.

A dependence between two statement instances belonging to statements  $S_i$  and  $S_j$  respectively, is represented by a set of equalities and inequalities in the *dependence polyhedron*,  $P_{e^{S_i \rightarrow S_j}}$ , where  $e^{S_i \rightarrow S_j} \in E$  is an edge in the Data Dependence Graph (DDG), G = (V, E), with each vertex representing a statement. The dependence polyhedron not only captures the iteration domain of the statements involved in the dependence, but also the exact dependence

Figure 2.4: Overview of the Polyhedral Framework

information such as which iterations are involved in the dependence. For example, in Figure 2.4c, the equalities express that there is dependence when i=l and j=k. The dependence polyhedron could express such a precise dependence relation because there existed an affine relation between the iterations and the referenced data.

Since the dependence polyhedron captures dependences among all loop iterations for affine programs, the dependence information in the DDG is *exact*. With this exact dependence information, the goal is to find a statement-wise multi-dimensional affine function (T) to represent a composition of loop transformations for the entire SCoP. Each dimension or level of this multi-dimensional affine function is represented by  $\phi(\vec{i})$  and is defined as follows:

$$\phi_S(\vec{i_S}) = (c_S^1 \ c_S^2 \ \dots \ c_S^{m_S})(\vec{i_S}) + c_S^0 \tag{2.3}$$

where  $i_S$  is the loop iteration vector for statement S, and  $c_S^0 \dots c_S^{m_S}$  are constants. Figure 2.4d shows the multi-dimensional affine functions  $(T_{S1} \text{ through } T_{S4})$  for each of the four statements of the *gemver* benchmark, where each function has 3 dimensions or levels represented by  $\phi^1$ ,  $\phi^2$ , and  $\phi^3$ , respectively.

The one-dimensional affine transform ( $\phi$ ) for each statement can either specify a *loop hyperplane* or a *scalar dimension*. A *loop hyperplane* is an n-1 dimensional sub-space of an n dimensional space represented by the normal  $(c_S^1 c_S^2 \dots c_S^{m_S}) \neq \vec{0}$ . A legal loop hyperplane corresponds to a loop in the transformed program. For example, for *gemver*,  $\phi_{S2}^2 = (1 \ 0)(i \ j)^T = i$ , and it represents a hyperplane that corresponds to the outermost loop (i-loop) for statement S2 as shown in Figure 2.4d. A legal hyperplane does not violate any unsatisfied dependence,  $e^{S_i \rightarrow S_j}$ , at that loop level, i.e.

$$\phi_{S_j}(\vec{t}) - \phi_{S_i}(\vec{s}) \ge 0, \langle \vec{s}, \vec{t} \rangle \in P_{e^{S_i \to S_j}}$$

$$(2.4)$$

where  $\vec{s}$  (source) and  $\vec{t}$  (target) are instances of statements  $S_i$  and  $S_j$ , respectively. The above condition implies the loop hyperplane preserves the direction of dependences between any two instances of statements  $S_i$  and  $S_j$ .

The above condition (2.4), when expanded becomes,

$$\left(c_{S_{j}}^{1} c_{S_{j}}^{2} \dots c_{S_{j}}^{m_{S_{j}}}\right) \vec{t} - \left(c_{S_{i}}^{1} c_{S_{i}}^{2} \dots c_{S_{i}}^{m_{S_{i}}}\right) \vec{s} \ge 0, \langle \vec{s}, \vec{t} \rangle \in P_{e^{S_{i} \to S_{j}}}$$

(2.5)

This is, however, non-linear in the unknown co-efficients of the phis and loop index variables. Thus, the affine form of the Farkas lemma is used for linearizing this legality condition as follows.

$$\left(c_{S_{j}}^{1} c_{S_{j}}^{2} \dots c_{S_{j}}^{m_{S_{j}}}\right) \vec{t} - \left(c_{S_{i}}^{1} c_{S_{i}}^{2} \dots c_{S_{i}}^{m_{S_{i}}}\right) \vec{s} \equiv \lambda_{e0} + \sum_{k=1}^{m_{e}} \lambda_{ek} P_{e}^{k}, \lambda_{ek} \ge 0$$

(2.6)

Thus, the non-linear form in terms of the loop variables (Equation 2.5) is now expressed as a non-negative linear combination of the faces of the dependence polyhedron through the use of Farkas lemma. Now, the coefficients (denoting a hyperplane) on the LHS and RHS can be equated to get rid of the loop variables. It is important to note that the legality condition has to be satisfied for every dependence in the SCoP, and thus Farkas lemma is also applied for every dependence. The resulting constraints (linear in the coefficients of the phis) are aggregated. For the purpose of eliminating the Farkas multipliers, Fourier-Motzkin elimination is employed.

In the polyhedral model, a fusion partitioning can be represented by a *scalar dimension* in the multi-dimensional affine function. For a scalar dimension,  $c_S^1 = c_S^2 = ... = c_S^{m_S} = 0$ ,  $\forall S$ , and  $c_S^0$  determines the partition number that the statement belongs to. The statements with the same value of  $c_S^0$  belong to the same partition, or in other words, they are fused at that loop level. For example, for *gemver*,  $\phi^1$  represents a scalar dimension, and statements S1 and S2 both have  $c_S^0 = 0$ , and as a result, they are perfectly fused in the transformed *gemver* code shown in Figure 2.4d. Since,  $c_S^0$  is 1 and 2, respectively, for statements S3 and S4, they are

distributed in the transformed code.

Thus, a multi-dimensional affine transform consists of multiple one-dimensional affine transforms representing legal loop hyperplanes interspersed by scalar dimensions. This multi-dimensional affine transform, because of the *convex combination* property, allows it to capture a sequence of simpler transformations such as coarse-grained parallelism, loop interchange, skewing, shifting, fusion and tiling. For example, in *gemver*, it allowed to capture parallelism, interchange and fusion in a single optimization step as seen in Figure 2.4d.

## **Chapter 3**

# **Tile Size Selection, from Then to Now**

#### **3.1 Introduction**

Loop tiling (8; 9; 10; 11) is a widely used loop transformation to enhance data reuse in higher levels of memory hierarchy. In essence, loop tiling reduces the *reuse distance* from being a function of the problem size to a function of the tile size. Loop tiling thus minimizes the *cache capacity* misses. However, tiling leads to non-contiguous data accesses in memory resulting in an increased probability of *conflict misses* in the cache. These conflict misses are a function of the tile size in tiled code. For example, for a problem size of (N=2000), a 2D tiled code of the *dsyr2k* kernel from BLAS library (12) with the tile size (TS<sub>1</sub>=8x128) performs 2.44x better than the one with the tile size (TS<sub>2</sub>=128x8) even though both codes have the same working set size in the L1 cache, when tested on an Intel Xeon processor based on the Sandy Bridge microarchitecture. One of the key reasons for this significant difference in performance is that the tile size TS<sub>2</sub> leads to pronounced conflict misses, that are 22 times more compared to those observed for tile size TS<sub>1</sub>.

Thus, tile size selection is critical to performance of the tiled code, and an optimal tile size is one which minimizes not only capacity but also conflict misses within a tile.

In the past, the problem of tile size selection has been attempted using analytical modeldriven approaches (13; 14; 3; 15; 16; 4; 17; 18). However, *these approaches have proved to be less robust because the models used did not fully capture the interaction between the source program (features like problem size and reuse characteristics of the arrays) and critical features in the modern processor microarchitecture such as multi-level and set-associative caches, and the*  *SIMD unit*. This has resulted in a widening gap between performance delivered by best known tile sizes and that achieved by using tile sizes predicted by the previous analytical models.

Tile size selection has also been widely studied using empirical auto-tuning as in ATLAS and PHiPAC for linear algebra (19; 20), FFTW and SPIRAL for Signal Processing (21; 22), ETile (23), and others (24; 25). However, each of these techniques is faced with a large search space of tile sizes when considering multidimensional, non-cubic tiling. For example, the size of search space for a level-3 BLAS kernel such as *gemm* scales at  $n^3$ , where n is a function of the size of cache being considered. If reuse opportunity in multiple levels of cache must be considered, the search space expands significantly for the larger caches, lower in the memory hierarchy. As a result, the adopted approach is either too time consuming (19; 21; 20; 22; 24) or less accurate when heuristics are used to reduce the search space (25).

In this work, we propose a new analytical model for selecting tile size in modern processors. The *Tile Size Selection (TSS) algorithm* proposed in our model chooses a tile size such that the following 4 objectives are met,

- it leverages the high set-associativity in modern caches to minimize interference and yield stable performance for all ranges of problem sizes in a variety of source programs.

- it considers data reuse at multiple levels of cache, which further boosts the performance of the tiled code.

- it considers the interaction of tiling with the SIMD unit on the host architecture and chooses a tile size that best benefits from it.

- it considers the impact of tiled code execution in a multithreaded environment (both chip multiprocessing and simultaneous multithreading environments) and achieves good performance.

Although the analytical model developed in this work chooses a particular tile size, it could also be used in conjunction with an auto-tuning framework to prune/navigate the search space.

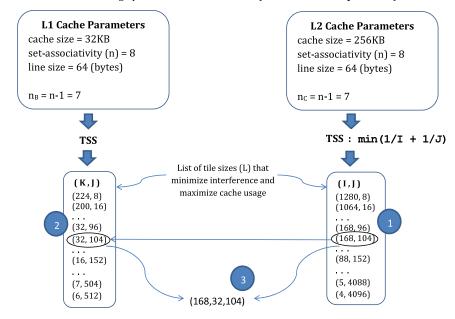

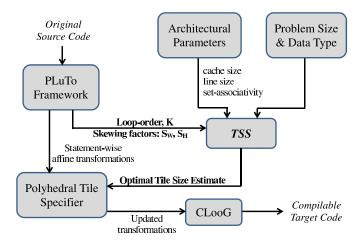

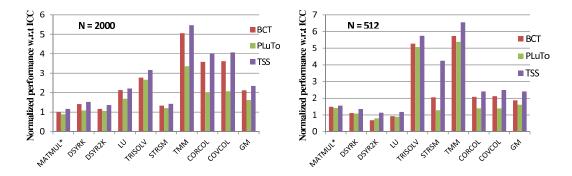

We implement the TSS algorithm within a source-to-source polyhedral compiler framework, PLuTo (26), which automatically tiles the source programs. For the generated tiled code, PLuTo chooses a cubic tile size by default. The TSS algorithm instead, estimates the optimal tile size which is then used by PLuTo to generate the corresponding tiled code. We tested our model on 12 benchmarks comprising a mix of linear algebra, data-mining and stencil kernels, all of which are known to benefit significantly from tiling. We tested each kernel with 2 different problem sizes on two different machines with different microarchitectures. Experimental results show that accommodating the impact of multi-level caches and the SIMD unit within the analytical model adds significant performance to the tiled code, and the tile size thus chosen is similar to that obtained from an exhaustive search for the best tiled code in a constrained search space. In comparison to the best square (cubic) tiled code for the test benchmarks, our tile size selection algorithm chooses tile sizes that perform 9.7% and 20.4% faster on average, respectively, for the 2 problem sizes. We also show that our model achieves good performance for tiled codes run in multithreaded environment using either the *chip multiprocessing* or the *simultaneous multithreading* technology.

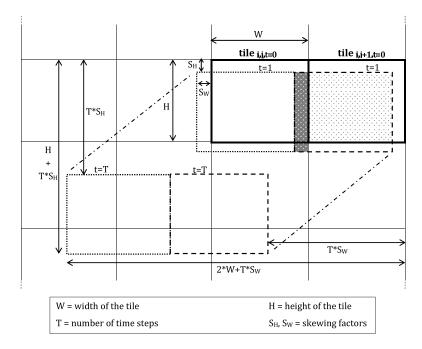

The rest of this chapter is organized as follows. Section 3.2 re-evaluates the problem of tile size selection from the point of view of a compiler via a case study and reinforces the motivation for this work. Section 3.3 discusses the multiple factors that influence tile size selection and explains our approach to accommodate them in our tile size selection model. In Section 3.4, we describe our algorithm for estimating the optimal tile size and discuss its scope. Section 3.5 describes the experimental setup and the benchmarks used for our experiments. We discuss the experimental results in Section 3.6. The related work is presented in Section 3.7. Finally, we conclude in Section 3.8.

#### **3.2** Motivation

Tile Size Selection has been deemed a complex problem from the point of view of a compiler. In this section, we re-evaluate the major reasons behind such a view and present a viable alternative to tackle the problem of tile size selection at compile time.

#### **3.2.1** Modeling the effect of set-associativity.